Chroma · 授权中国一级代理商

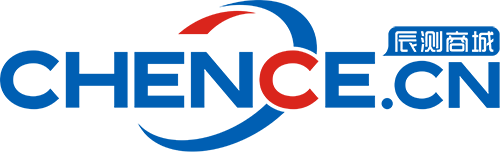

- 8 channels of arbitrary waveform generator (AWG) and 8 channels of digitizer (DGT) per board

- Provide high frequency mode and high resolution mode for both AWG and DGT

- AWG

- 16 bits high frequency DAC with 400Msps

- 24 bits high resolution DAC with 2Msps - DGT

- 16 bits high frequency DAC with 250Msps

- 24 bits high resolution DAC with 1.5Msps - V Reference Source

- Individual two channels per rider

- 20 bits resolution, voltage range from -1V ~ 6V

- Settling time: 1ms; Max output current: 10mA

- Four wires connection - Build in precision PLL clock per rider with 250fs Jitter

- Selectable filter range

- 120MHz bandwidth for high frequency mode

- Four channels of precision measurement unit (PMU) per board

- Can be allocated to any universal slot

- Support external trigger input per rider

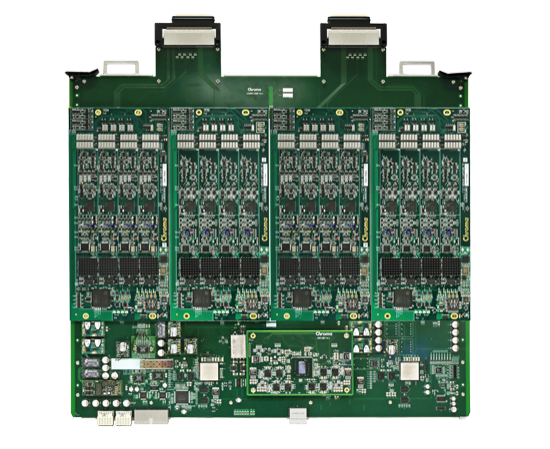

- Support on 3680 SoC System

- GUI Setup and programmable in CRISPro software environment

Target Application

- Consumer/Portable Audio

- STB

- Digital TV

- Video Converter

- xDSL/Cable Modem

- baseband

The HDAVO is an optional mixed-signal module that can provide source and capture test capabilities with Arbitrary Waveform Generator (AWG) and Digitizer (DGT) functions when integrated into the 3680 SoC test system. The module has 8 AWG and 8 digitizers on an instrument board which can be allocated to any universal slot in the 3680 SoC system. With a maximum of 120MHz instrument bandwidth and density, it can meet the performance required by a wide range of device types. Building either in audio or video band on each channel, the module can accomplish multisite testing with lower cost.

The HDAVO achieves the I/Q phase and amplitude matching with better 25ps channel to channel skew through a dedicate external calibration board. This enables the system to test a wide range of I/Q modulator standards such as 802.11a/b/g/n wireless LAN and cellular baseband processor.

The CRISPro software environment provides a power ful tool for the user to setup the HDAVO via a Graphic User Interface (GUI). The coding based with user friendly environment can produce test programs quickly and easily to implement concurrent functions for complex and multi-function SoC device with lower cost of test (CoT) requirement.